**Total Number of Pages: 02**

M.Tech P1ELBC04

1<sup>st</sup> Semester Regular Examination 2017-18 INTEGRATED CIRCUIT DESIGN **BRANCH: ELECTRICAL AND ELECTRO ENGG**

> Time: 3 Hours Max Marks: 100 **Q.CODE: B1013**

Answer Question No.1 which is compulsory and any FOUR from the rest. The figures in the right hand margin indicate marks. Assume values wherever missing

## Q1 Answer the following questions:

$V_{SG}=V_{DD}$ .

$(2 \times 10)$

- Show graphically that as the bias current, Ibias, decreases in an active load inverter, the gain increases for some time and then it becomes independent of Ibias.

- Draw the circuit of a cascode with cascode load.

- c) Implement a SR Latch using CMOS.

- d) What are Mixed Signal Systems? What is an ATE?

- e) What is HEMT? Mention one of its applications.

- What is ATE? What are its main components?

- g) Draw the layout diagram for the CMOS logic implementation for the given logical function Q = AB(CD + CE) + F.

- h) Implement a SRAM cell using CMOS logic.

- Why PMOS is used as pull up network and NMOS as pull down network?

- What is voltage reference circuit? Write down different techniques used in reference j) circuits?

- (10)Q2 a) (i) For a CMOS inverter with the following parameters: $V_{DD} = 3V$ ,  $V_{TD} = 0.6V$ ,  $V_{TD} = 0.6V$ -0.82V, k' =  $100\mu$ A/V<sup>2</sup>,  $\mu_n$  =  $2.2\mu_n$ : Determine the beta ratio, ßn/ßp, for a midpoint (switching threshold) of V = 1.3V. Also determine the relative device widths, Wp/ Wn, for V = 1.3V. (ii) A pMOS transistor of W=3μm and L=0.6μm has parameters tox= 500nm, surface mobility  $\mu_n = 200 \text{ cm}^2/\text{V} - \text{sec}$  and threshold voltage  $V_{tp}$  = -0.6V.  $V_{DD}$  = 3V. Calculate the transistor transconductance,  $\beta p$ . Also estimate the channel resistance,  $R_p$ , at

- b) Define Noise Margins. Derive the Noise Margin for a symmetrical CMOS Inverter.

- Q3 a) Calculate the input and output impedance of a Source Follower.

(10)(10)

(10)

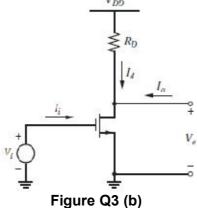

**b)** Find the voltage gain of the common-source amplifier of Figure Q3 (b) with  $V_{DD} = 5V$ ,  $R_D = 5k\Omega$ ,  $k' = \mu_n C_{ox} = 100\mu A/V^2$ ,  $W = 50\mu m$ ,  $L = 1\mu m$ ,  $V_t = 0.8V$ ,  $L_d = 0$ ,  $X_d = 0$ , and  $X_t = 0$ . Assume that the bias value of V<sub>i</sub> is 1 V.

| Q4 | a)       | Explain the concept of Dynamic gate? Explain with an example. What are the issues in Dynamic Design?                                                                                | (10)         |

|----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | b)       | Discuss different types of Current Mirror Circuits.                                                                                                                                 | (10)         |

| Q5 | a)<br>b) | Explain datasheets? Explain the different components of test program  Define line regulation, load regulation, input impedance, and output impedance?  Explain DC gain measurement? | (10)<br>(10) |

| Q6 | a)<br>b) | What is FinFET? Discuss its construction and uses. Write short notes on Floating gate MOS and Organic FET?                                                                          | (10)<br>(10) |

| Q7 | a)       | For a Cascode Amplifier, draw its small signal equivalent and give the value of its $V_{bias}$ . Also calculate its gain.                                                           | (10)         |

|    | b)       | How will IC Design impact Internet of Everything?                                                                                                                                   | (10)         |