|     |       |                                                           |                      |                                        |                                                              | 1                            | 1                                           |                               |                   |         | <del>                                     </del> |                    |

|-----|-------|-----------------------------------------------------------|----------------------|----------------------------------------|--------------------------------------------------------------|------------------------------|---------------------------------------------|-------------------------------|-------------------|---------|--------------------------------------------------|--------------------|

|     | F     | Registration no:                                          |                      |                                        |                                                              |                              |                                             |                               |                   |         |                                                  |                    |

| Tot | al Nu | mber of Pages: 04                                         | ı                    |                                        |                                                              |                              |                                             |                               |                   |         |                                                  | M .TECH<br>VLPC101 |

|     |       | 1 <sup>st</sup> Semes  Answer Questio The fig             | HI<br>Bran<br>n No.1 | DL and<br>nch: VI<br>N<br>Que<br>which | l High<br>LSI& I<br>Fime: 3<br>Max ma<br>stion C<br>i is con | Level Embe B Hou arks: Code: | l Syn<br>dded<br>irs<br>70<br>T119<br>ory a | thesis<br>Syte<br>2<br>and an | s<br>ms<br>ny fiv | ve fro  | m the                                            |                    |

|     |       | The fig                                                   | ui es ii             | i the ii                               | igiit iia                                                    | nu m                         | argn                                        | ı muı                         | Cate              | IIIai K | .5.                                              | (2 x 10)           |

| Q1  | a)    | Answer the follow<br>What is a Hardwa<br>programming lang | re Des               |                                        | Langu                                                        | age? I                       | How i                                       | s it d                        | iffere            | nt fro  | m a no                                           | rmal               |

|     | b)    | Given SIGNAL a : BIT :: SIGNAL b : BIT_ SIGNAL c : BIT_   | VECTO                |                                        |                                                              |                              |                                             |                               |                   |         |                                                  |                    |

|     |       | Fill up the following                                     | ng blanl             | ks:                                    |                                                              |                              |                                             |                               |                   |         |                                                  |                    |

|     |       | $x1 \le a \& c;$<br>$x2 \le b sll 2;$                     |                      |                                        | :                                                            |                              |                                             |                               |                   |         |                                                  |                    |

|     | c)    | Enlist some concure each).                                | rrent an             | d some                                 | sequen                                                       | tial sta                     | iteme                                       | nts of                        | VHD               | L. (At  | least tv                                         | vo                 |

|     | d)    | Give examples of                                          | a block              | stateme                                | ent. Wha                                                     | at is a                      | guard                                       | led blo                       | ock?              |         |                                                  |                    |

|     | e)    | (i) There are two f<br>this exemplify?                    | unction              | s with t                               | he same                                                      | name                         | e. Whi                                      | ich fea                       | ature (           | of VI   | IDL do                                           | es                 |

|     |       | (ii) Given two fund                                       | ctions:              |                                        |                                                              |                              |                                             |                               |                   |         |                                                  |                    |

|     |       | function check_lin                                        |                      |                                        | _                                                            |                              |                                             |                               |                   |         |                                                  |                    |

|     |       | Now if we call the test1 := check_lim test 2:= check_lim  | it(4095              | )                                      |                                                              | lowing                       | g state                                     | ements                        | 3                 |         |                                                  |                    |

f) Differentiate between Sequential Signal assignment statements and Concurrent Signal Assignment statements.

g) Differentiate between Identifier and reserved word with example.

Identify which function will be called when.

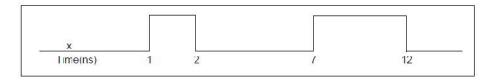

h) 5 Waveform of signal X is given below .Sketch the waveform for Y and Z for

following assignment.

Y <= transport X after 2ns;

$Z \le X$  after 2ns;

- i) Differentiate between port mapping by name and port mapping by position.

- j) Give the enumeration type definition for a four-valued system 0, 1, X, Z.

- Q2 a) Find at least five errors in the following code:

(5)

Library ieee;

Use ieee.std\_logic\_1164.all;

Entity Q2 is

ports( DATA : in std\_logic\_vector(7..0);

CARRY :in std\_logic;

result :out BIT);

end Q2;

architecture Q2 of Behavioral is

signal MODE : std\_logic\_vector(3 downto 0);

begin

MODE => DATA(6 downto 4);

With MODE select

RESULT <= CARRY when "0000",

'1' when "0001",

'0' when "1000";

Y <= CARRY and result;

End Behavioral:

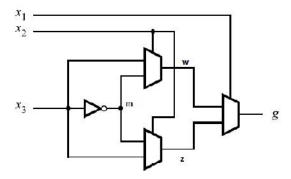

b) Write a VHDL description of the following circuit. Derive the logic function g represented by the circuit. (5)

Q3 a) Write VHDL code that represents a T flip-flop with an asynchronous clear input. (5) Use behavioral code, rather than structural code.

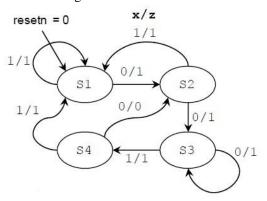

b) Write the VHDL code for the given state machine.

(5)

Q4 Suppose that the operations that we want to implement in an ALU are as defined (10) in Table below. The xi column shows the values that the output, LE must generate for the different operations. The yi column shows the values that the output, AE must generate. The c0 column shows the carry signals that the output, CE must generate. Implement this ALU using VHDL.

| 52 | 5] | 50 | Operation Name | Operation        | $x_i$ (LE) | $y_i(AE)$ | c0 (CE) |

|----|----|----|----------------|------------------|------------|-----------|---------|

| 0  | 0  | 0  | Pass           | Pass A to output | a;         | 0         | 0       |

| 0  | 0  | 1  | AND            | A AND B          | a: AND b;  | 0         | 0       |

| 0  | 1  | 0  | OR             | A OR B           | a; OR b;   | 0         | 0       |

| 0  | 1  | 1  | NOT            | A'               | $a_i$      | U         | U       |

| 1  | 0  | 0  | Addition       | A + B            | $a_i$      | $b_{r}$   | 0       |

| 1  | 0  | 1  | Subtraction    | 1 B              | $a_i$      | b,'       | 1       |

| 1  | 1  | 0  | Increment      | A+1              | $a_i$      | 0         | 1       |

| 1  | 1  | 1  | Decrement      | A-1              | $a_i$      | 1         | 0       |

- Q5 a) Make a Comparison between the VHDL Constructs-WHEN and CASE by taking (5) a 2-to-4 decoder circuit as an example.

- b) Discuss the Simulation System in CAD design with suitable block diagrams. (5)

- Q6 a) Complete the timing diagram of the circuit whose VHDL description is shown (5) below. Also draw the circuit.

library ieee;

use ieee.std\_logic\_1164.all;

entity circ is

port ( resetn, x, clk: in std\_logic;

q: out std\_logic);

end circ;

architecture a of circ is

signal qt: std\_logic;

begin

process (resetn, clk, x)

begin

if resetn = '0' then

qt <= '0';

```

elsif (clk'event and clk '0') then

if x = '1' then

qt <= not(qt);

end if; end if;

end process;

q <= qt;

end a;</pre>

```

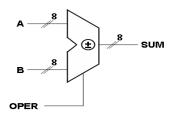

b) An unsigned 8-bit Adder/Subtractoris shown in the Figure below. Write the VHDL codes for this unsigned 8-bit Adder/Subtractor. (5)

| I/O Pins | Description      |  |  |

|----------|------------------|--|--|

| A, B     | Add/Sub Operands |  |  |

| OPER     | Add/Sub Select   |  |  |

| SUM      | Add/Sub Result   |  |  |

- Q7 a) Draw the logic diagram and write VHDL structural model code for 4-bit binary (5) comparator.

- b) Consider the VHDL process shown below.

Q

process (a, b, c) begin  $x \le a$  and b; if a < b then  $y \le b + c$ ; elsif b > c then

$$x \le a \text{ xor } c; y \le \text{`1'};$$

else

$y \mathrel{<=} a;$  end if;

end process;

Draw a circuit directly from the VHDL that implements this process (do not derive simplified equations for this part). Your circuit may include XOR gates ans d 2:1 MUXs.

Q8 Write Short Notes on any two of the following:

(5 X 2)

(5)

- a) The ASIC Design Process.

- b) CAD tools and its functions

- c) Datapath-Controller design

- d) 32 bit ROM implementation

- e) Functions and Procedures